INTERDATA

MODEL 80

FUNCTIONAL SPECIFICATION

Revision 0 August 2, 1971 Revision 1 September 14, 1971

#### TABLE OF CONTENTS

#### 1.0 INTRODUCTION

- 1.1 Packaging

- Processor 1.2

- 1.3 Main Memory

- 1.4 I/O System

- 1.5 Expansion Control Store

- 1.6 Power Supply

#### 2.0 SUMMARY OF CHARACTERISTICS

- 2.1 User Memory

- 2.2 Control Memory

- 2.3 User Instructions

- 2.4 Micro Instructions

- 2.5 Internal Modules

- 2.6 Peripherals

- 2.7 Interrupts

- 2.8 Registers

- 2.9 Processor Timing

#### SYSTEM DESIGN PHILOSOPHY 3.0

# FUNCTIONAL DESCRIPTION OF THE BASIC CPU

- A, B, S and Control Busses

- A(0:15), B(0:15), S(0:15)

- 4.3 Typical Bus Exchange

- Control Module (CU) 4.4

- Arithmetic Module (ALU) 4.5

- 4.6 I/O Interface Board

#### MICROPROGRAMMING 5.0

- 5.1 Module 0

- 5.2 Non-CPU Instructions

- 5.3 Micro-Control

- 5.4 Control Store Data Storage

- 5.5 Interrupts

- 5.6 Registers

- 5.7 Arithmetic Module (ALU) Programming5.8 I/O Module Programming

- 5.9 CPU Flags

#### 6.0 MEMORY SYSTEM

- 6.1 Introduction

- 6.2 System Main Memory

- 6.3 Read Only Control Memory

6.4 Dynamic Control Store Memory

6.5 Special Configuration

- 7.1 Configuration and Power7.2 Basic Processor Chassis7.3 Special Maintenance Considerations

- 7.4 Power Supplies

- 8.1 Maintenance Facilities

- 9.1 Peripheral Device Controllers

#### 1.0 INTRODUCTION

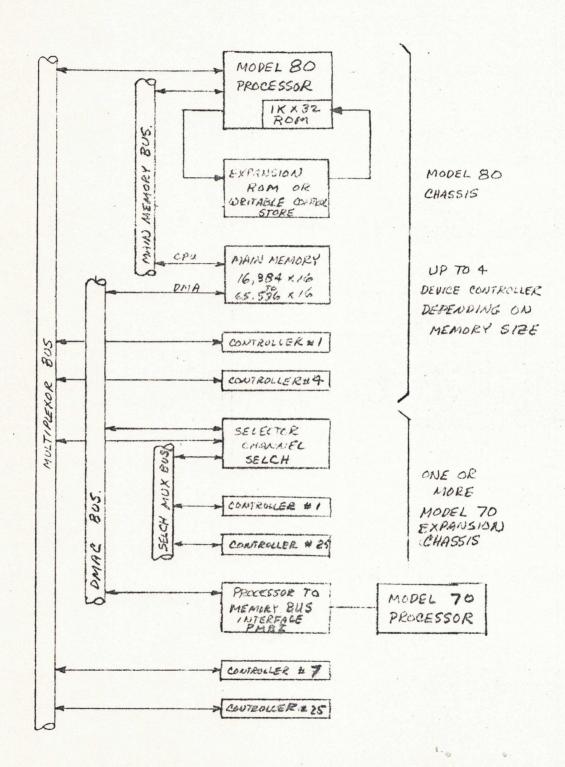

The Model 80 system is a high performance member of the INTERDATA family of computers with performance 3 to 6 times that of a Model 70. It is strictly compatible with the Model 5 and 70 systems from both hardware and software points of view.

All software generated for the Model 5 and 70 systems will run on this system.

All peripheral devices, 10" or 15"/7" designs, will interface to this system.

The packaging is the same as that of the Model 70. 15" card files, 8 cards per file.

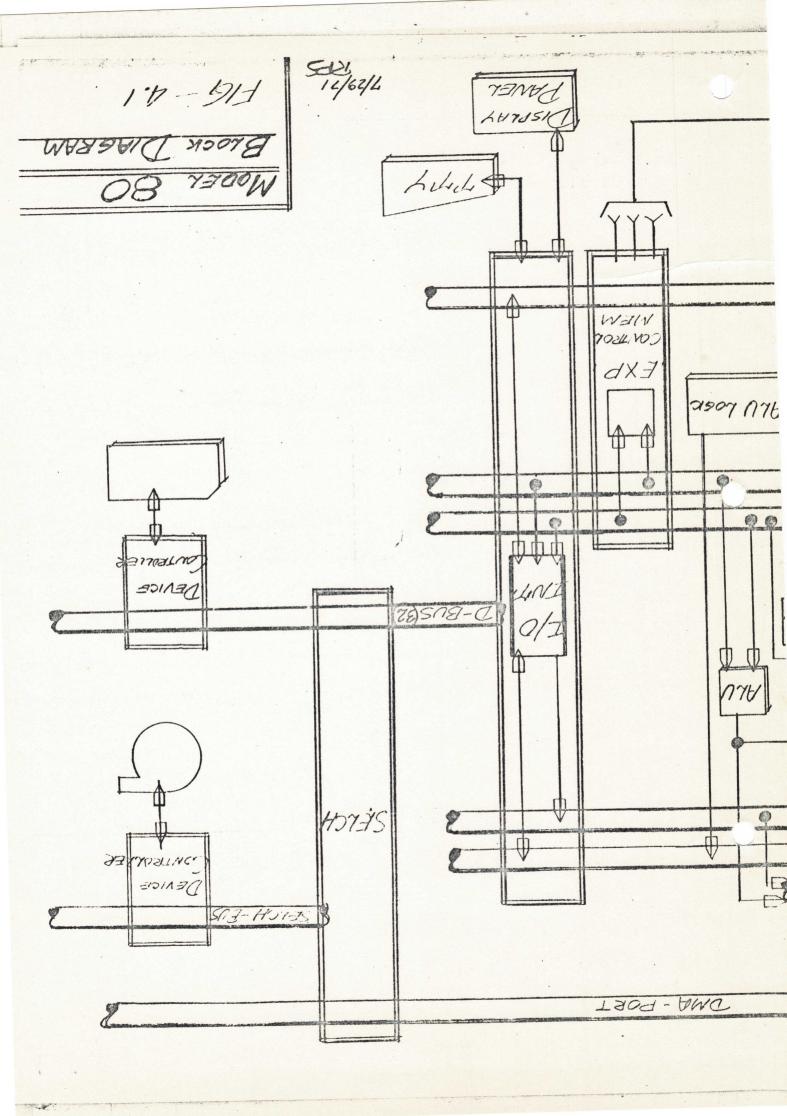

The expansion chassis used for I/O will be identical to that used in the Model 70.

The specifications and features of the system are breifly described below and will be covered in detail in the following chapters.

# 1.1 Packaging

The Model 70 packaging and display panel will be used. The Model 80 with up to 64K of core will mount in one card file.

## 1.2 Processor

The Processor consists of a double card assembly CPU/ALU and an I/O card which generates the I/O bus and contains the display controller and TTY controller. The CPU employees a 32 bit instruction word and 16 bit bussing. The basic clock rate is 10 MHz. User level instruction execution times will be typically 450 ns for RR and RS and 900 ns for RX. The basic instruction set will be contained in 768 words of ROM.

## 1.3 Main Memory

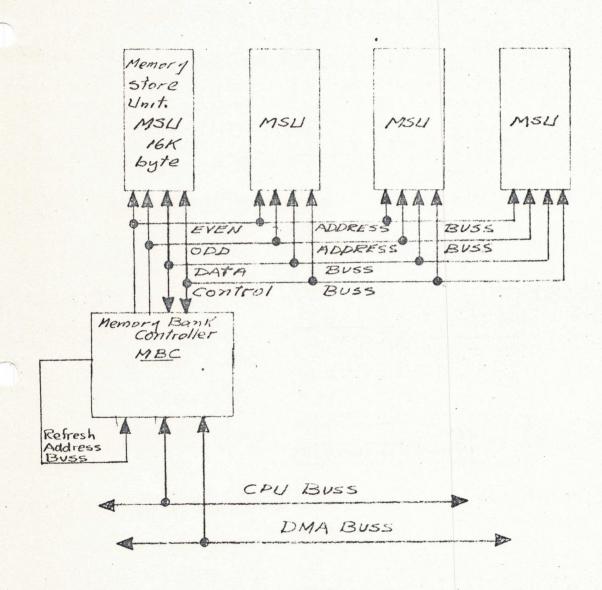

The main memory uses MOS/LSI devices for storage. It has an effective cycle time of approximately 220 ns. Memory banks can be accessed via the Processor or through an external DMA port. The xternal port has a through-put of approximately 9 megabytes/sec. or may be used as a multiplexed port by up to four devices at a maximum through-put of 5.2 megabytes/sec. The packaging consists of a single 15" memory controller and one-four storage modules of 16K bytes each, cabled directly to the controller. The DMA connections is via the back panel. The DMA port will accommodate the Model 70 selector channel in the multiplexed configuration.

## 1.4 I/O System

The I/O system is identical to Model 70 and will use the same packaging. The basic processor with minimum memory will accommodate three 15" I/O cards, in addition to the TTY and display.

# 1.5 Expansion Control Store

The basic Model 80 uses 768 words of ROM control store which is mounted on the CPU/ALU board. Room is provided to mount an additional 256 words of ROM on this board. The control store may be expanded by another 3K words of either dynamic control store (DCS) or ROM by adding additional circuit boards. Two new user instructions are added for manipulating the DCS.

#### 1.6 Power Supply

The volatile semiconductor Main Memory of the Model 80 will be powered by a separate supply that includes built-in battery backup for short term power interrupts and facilities for low power stand-by operation of the memory when the system is shut down. The internal battery will be capable of holding the memory's contents, in the low power non-operating mode, for several minutes. For long term memory protection, the customer will be required to supply 115/230 VAC (+20% @ 47-63Hz). Readily available DC to AC inverters can be used. (The 115/230 volts is required to power fans in the power fail situation.)

The memory will go into the low power stand-by mode whenever the processor is shut down. It will not use the battery or the reliable AC source, however, except on a primary power failure. The Memory Power will not be controlled by the front panel power switch.

The Model 80 Processor, Control Memory, and I/O will use any of the Power Supplies available with the Model 70 system.

#### 2.0 SUMMARY OF CHARACTERISTICS

The speed and capability of the Model 80 can be best outlined by a summary of its characteristics.

#### 2.1 User Memory

- low power MOS semiconductor LSI design

- 250 ns access by CPU

- individual ports for CPU and DMA

- expandable in 16KB increments to 64KB

- multi-bank capability

- built-in instruction look-ahead for CPU

- built in emergency 'keep-alive' power supply and auxiliary power switching

## 2.2 Control Memory

- bipolar 50 ns semiconductor ROM

- directly addressable to 4K instruction

- dynamic control store memory available on some models

- data storage in dynamic control store memory permits vary fast matrix manipulations, function generation, etc.

- asynchronous timing allows dynamic control store memory to be any speed

## 2.3 User Instructions

The Model 80 is upward compatible from the Models 3, 4, 5 and 70 at the user instruction level. Specifically, it will implement the same instructions as those of the Model 70 plus those necessary to manipluate the dynamic control store in the micro-level computer on those versions so equipped.

Although the timing of the individual instructions vary somewhat, the following lists the typical speeds for different classes of user instructions. A complete list is given in the appendix.

|    | GENERAL | MULTIPLY/DIVIDE | SHIFT/ROTATE | BRANCH   | FLOAT<br>ADD | FLOAT<br>MULTIPLY |  |

|----|---------|-----------------|--------------|----------|--------------|-------------------|--|

| SF | 450     |                 | 450-1900     | 450-1450 |              |                   |  |

| RR | 450     | 2100            |              | 450-850  |              |                   |  |

| RS | 450     |                 | 450-1900     | 450-850  |              |                   |  |

| RX | 900     | 2500            |              |          | 13.61        | 19.1              |  |

FIGURE 2.1 USER INSTRUCTION TIMING (NANOSECONDS)

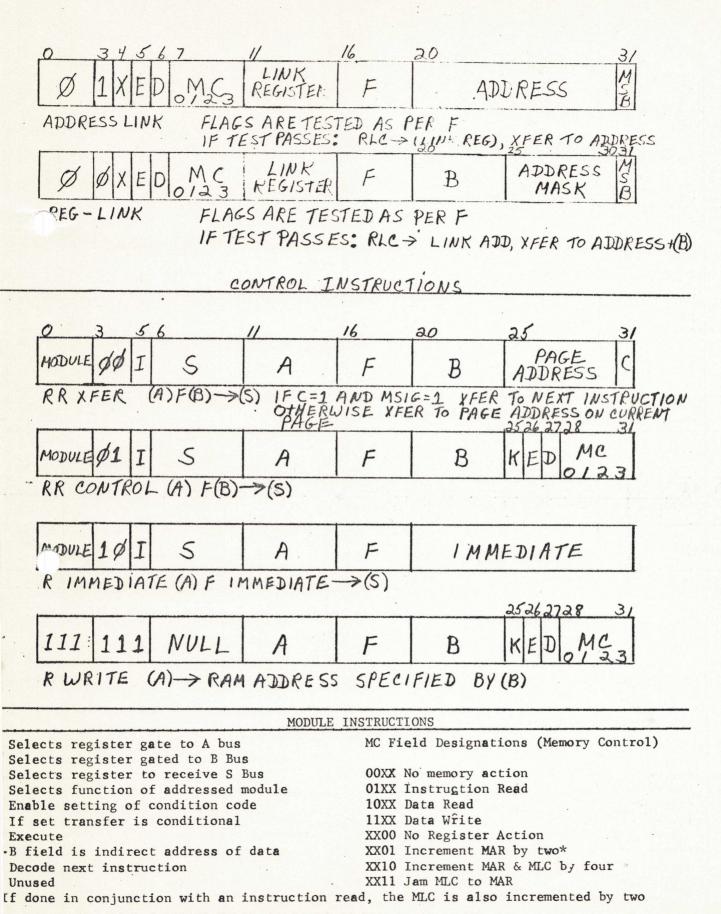

#### 2.4 Micro Instructions

The micro instruction word is 32 bits long. In addition to the branch and write instructions, there are three types of instructions to the internal modules. These minimally encoded instructions provide 112 combinations of module/function commands. The micro-instruction can simultaneously direct two operands and a result independently on three of the computer's busses, generate 12 bit immediate field operands, select the address of the next micro instruction, and perform non-encoded micro control of the computers functions such as reading/writing main memory, incrementing user location and memory address registers, controlling the user status register, and decoding the next user instruction.

<sup>1.</sup> micro-seconds

## 2.5 Internal Modules

The Model 80 hardware architecture will accommodate eight internal modules which communicate over three of the Processor busses.

In theory, the function of all of the modules (with the exception of the control module) is arbitrary, and the significance of the various instructions take meaning only when applied to a specific module.

The basic Model 80 is composed of a control module (which controls the user memory, control memory, register gating and instruction sequencing) an arithmetic/logic module (capable of 20 operations including hardware multiply/divide and multiple position shifting), and an I/O module (which connects the internal busses of the Processor to the standard INTERDATA Multiplexor (I/O) bus.)

The architecture will accommodate five additional arbitrary modules such as floating point, boolean manipulors, or special nature designs.

# 2.6 Peripherals

The Model 80 will interface to, and is compatible with, all standard INTERDATA peripheral controllers and controllers designed to the standard INTERDATA Multiplexor bus. Any number of devices up to 255 can be accommodated, but a maximum of 16 can be interfaced directly to the Multiplexor Bus or the Selector Channel's bus (based on the new interface standards).

#### 2.7 Interrupts

The Model 80 has eight hardware priority interrupts, most of which can be masked by various bits of the PSW. The occurrence of a recognized interrupt causes the micro-program to 'trap' to one of eight specific control store locations associated with the interrupts.

#### 2.8 Registers

The Model 80 has 16 general registers, 15 of which may be used as index registers. In addition, there are eight additional general purpose registers available to the microprogrammer, plus 5 registers associated with the user level machine control that are available to the micro-programmer.

## 2.9 Processor Timing

Communications between modules is request/response. Timing is completely asynchronous (rather than quantized) to achieve maximum speeds. Additionally, interlocks are provided between the control memories and the CPU to facilitate programming the micro machine. The control module operates on a 10MHz clock, allowing a minimum instruction execution in 200 ns. Internal timing within the other modules can be selected to best suit the needs of the module.

#### 4.0 FUNCTIONAL DESCRIPTION OF THE BASIC CPU

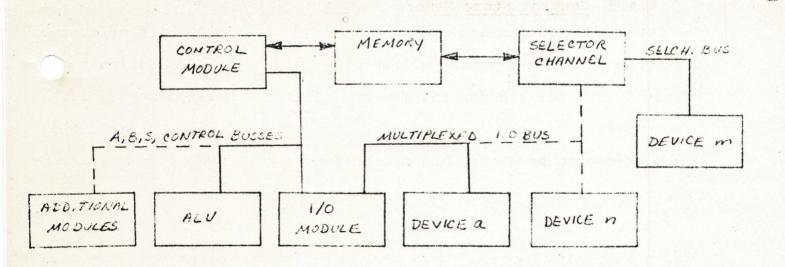

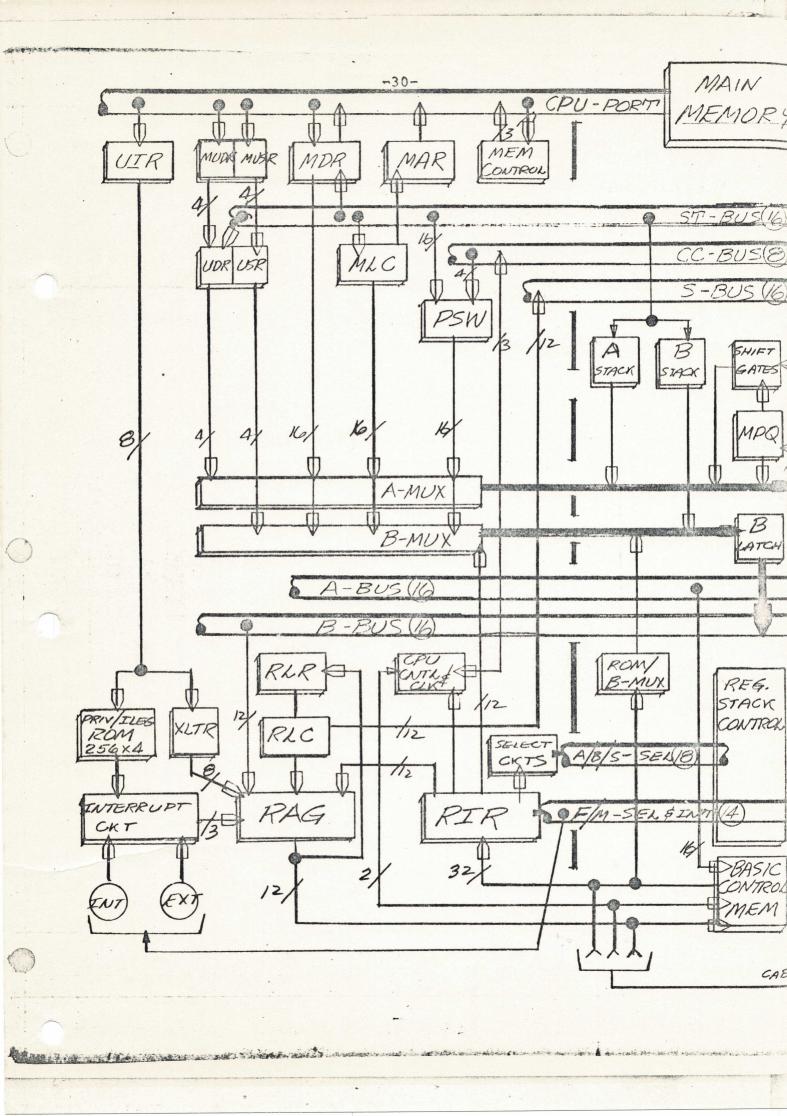

The functional characteristics of the CPU can best be described in terms of its registers, busses and related gating. (Refer to Figure 4.1.) There are four busses which are key to the modular design philosophy of the architecture. An understanding of the bus tructure is necessary to determine how each module of the processor interrelates and further how the registers and gating of each module contributes to the function which the module is designed to serve.

# 4.1 A, B, S and Control Busses

The control bus of the computer is commanded by the control module and in essence is a reflection of that segment of the micro instruction selecting the function and module to be addressed, plus timing to effect transfers of data. Lumped into this also is a means for a module to transfer data to the condition code of the PSW. Following is a description of the control bus signals (shown individually on igure 4.1).

- a. Module Select Lines (MDSEL [0:2]) These three lines contain the address of a module for which the current micro-instruction is intended. One of the eight arbitrary modules can be selected by the instruction to perform some function. These three lines reflect bits (0:2) of the micro-instruction.

- b. Function Select Lines (FSEL [0:3]) These four lines reflect bits 16:19 of the micro-instruction and normally select one of sixteen arbitrary functions to be performed by the selected module.

- c. Start (STRT) STRT signals the internal modules that data is valid on the busses. It is in effect a request from the control module for a response to a micro-instruction.

Data is held static on the A & B busses while STRT is active. The control module holds STRT active until it recognizes a response from the module (MFIN) and has stored the results presented on the S Bus.

- d. Module Finished (MFIN) MFIN is a response to the control module from a selected module indicating that it has recognized STRT and completed the selected function. The selected module gates data and other responses onto the S bus prior to returning MFIN. Data and responses must be held on the busses until the control removes STRT. This time is indefinite and depends on events within the control module.

- e. Module Signal (MSIG) This is a control signal manipulated by the selected module to indicate some arbitrary condition to the control module. It is tested by the control module during a normal micro-instruction to the selected device to control a conditional branch in the micro-program.

- f. Condition Code Bus (SCC, VCC, CCC, GCC, LCC)

SCC signals the control module that the selected module

wishes to manipulate the condition code of the program

status word. If the micro-programmer has enabled this

manipulation, the condition code is forced to a status

specified by the selected module. The status is uncondition

ally forced into the CPU flags. This is done concurrent with

a normal instruction to the selected module.

g. VCC, CCC, GCC, LCC - These lines specify the status forced into the condition code of the program status word and represent overflow, carry, greater than, and less than, respectively.

# 4.2 A (0:15) B (0:15) S (0:15)

The A, B and S busses are the primary data links between the control and the selected module. Gating of data to/from each of these busses is controlled by the micro-instruction. Almost all the registers of the control module can be gated to/from these busses.

Data is selected by the micro-instruction from two independent sources and transmitted to a selected module over the A & B busses. The module is thus presented simultaneously with two operands. The resulting data is returned to the control module via the S bus. The destination of the S bus is selected by the micro-instruction.

# 4.3 Typical Bus Exchange

The use of these busses can be summarized by an example.

- 1. The micro-instruction selects a module (MDSEL 0:2) and directs it to perform some function (FSEL0:3).

- 2. The operands are selected from somewhere in the control module and gated onto the A and B busses.

- 3. The control module informs the selected module that all data if valid on the busses and that it may begin (STRT).

- 4. The selected module performs the function (S) = (A) F (B) and gates the results to the S bus.

- 5. The selected module may manipulate the condition code via SCC-VCC-GCC-LCC-CCC.

- 6. The selected module may signal that the result of the operation was zero (for example) by activating MS1G.

- 7. The selected module activates MFIN to signal the CPU module that the operation is complete and the results are presented on the S bus.

- 8. The control module recognizes MFIN, gates the S bus to the destination specified by the micro-instruction, and then removes STRT.

- 9. The selected module deactivates itself when STRT is removed.

## 4.4 Control Module (CU)

- 4.4.1 Registers. The following registers are part of the control module although some may reside physically within the ALU.

- a. A Stack, B Stack: The A stack and B stack are a redundant set of register banks containing the twenty-four general purpose registers of the CPU. The registers are duplicated to allow simultaneous gating of any register in the stack onto either the A bus or the B bus. Sixteen of these registers are the user general registers; while the remaining eight are available to the micro-programmer as desired. These registers are gated onto the A and B bus and loaded from the S bus under control of the micro-instruction.

- b. Memory Data Register (MDR): This register provides

the data buffer between the CPU and the user level memory.

The MDR can be gated onto the A and B busses and loaded from

the S bus under control of the micro-instruction. It is,

of course, also loaded under control of the memory when a

memory read cycle is requested. Hardware interlocks are

employed to synchronize the memory to the CPU.

- c. Memory Location Register (MLC): The MLC is a general purpose register which can be gated to either the A or B bus and loaded from the S bus, but posesses additional characteristics intended to facilitate the emulation of the user level repertoire. The register can, under microcontrol, be incremented by two, incremented by four, and jammed into the memory address register. This register keeps track of the current instruction location of the emulated machine.

- d. Memory Address Register (MAR): This register contains

the address of user memory the micro-programmer is reading

or writing. It can be loaded from the S bus under control

of the micro-instruction, or loaded from the MLC, or incremented

by two, or incremented by four under micro-control. The

least significant bit of the MAR is used to control byte

steering for the byte-oriented instructions of the user

repertoire (refer to Section 4.6). As in the MDR, timing

conflicts are resolved by hardware interlocks.

- e. Program Status Word (PSW): The program status word is a 16-bit register which may be gated onto either the A or B bus and loaded from the S bus under control of the microinstruction. Various bits of the PSW are used to enable associated hardware interrupts. PSW (12:15) contain the condition code of the user level computer. These bits may be compared and tested against corresponding bits of the user instruction under Module O micro-instructions to effect emulation of user branch instructions. Additionally, they can be manipulated by any module designed to do so, if they are enabled by the micro-programmer.

- f. User Destination Register, User Source Register (UDR, USR):

These two control registers store bits (9:11) and (12:15),

respectively, of the current user level instruction being

emulated, and allow the micro-programmer to indirectly

reference the general registers selected by the user instruction. The UDR is compared to the PSW condition code on

certain micro-instructions to emulate user level branches.

Both registers can be examined by gating them onto the A bus under micro-instruction control. The UDR can also be loaded from the S bus.

- g. User Instruction Register (UIR), Memory User Destination Register (MUDR) and Memory User Source Register (MUSR).

These three registers are loaded with bits (0:7), (8:11), and (12:15), respectively, of the next user level instruction to be emulated. The eight bit opcode stored in the UIR is used to vector to the emulation sequence for the next user instruction. It is also used to interrogate a ROM which has been configured to decode privileged and illegal user level instructions. The contents of the MUDR and MUSR are transferred to the UDR and USR at the beginning of the next emulation.

- h. ROM Location Register (RLR): This register stores the current address of the control store instruction. It is loaded from the ROM address gates (RAG) at the beginning of every instruction except interrupt trap instructions and 'execute' type instructions (explained in chapter on micro-programming). The RLR is a (12) bit register allowing direct addressing of control store up to 4K instructions.

- i. ROM Instruction Register (RIR): This (32) bit register stores the current micro-instruction. The RIR is the focus of control of the CPU.

- j. A Latch, B Latch: The A latch and B latch registers, as their name implies, latch the data presented by the control module to be gated onto the A and B busses. They are the data sources for these busses.

## 4.4.2 Interrupts

The hardware of the computer provides eight priority interrupts. Each interrupt has a unique 'trap' location associated with it. Recognition of an interrupt causes the instruction stored at its respective trap location to be performed. The RLR contents are preserved to allow the address of the interrupted sequence to be saved if desired so that control can be returned at the completion of the interrupt outine. Certain interrupts are enabled/disabled by bits of the PSW as shown in Figure 4.2. Additionally, all interrupts can be enabled/disabled as a group by micro-instruction. All interrupts not masked by PSW bits are interrogated when a new user level instruction is decoded, regardless of the status of the group enable. enable is automatically disabled at the beginning of a user emulation, and must be enabled by instruction if the programmer wishes to recognize the group enabled interrupts within an emulation sequence. The following table lists the pertinent information for each interrupt. The external interrupts 1, 2 and 3 will cause an EXTERNAL INTERRUPT.

|                  | INTERRUPT                        | TRAP | MASK  |       |          |

|------------------|----------------------------------|------|-------|-------|----------|

|                  | Primary Power Fail               | 0616 | NONE  |       |          |

|                  | Machine Malfunction <sup>1</sup> | 0516 | PSW02 |       |          |

|                  | Display                          | 0416 | NONE  |       |          |

|                  | Ext. Interrupt                   | 0316 | PSW01 | (DATA | CHANNEL) |

| A Service of the | Ext. Interrupt                   | 0216 | PSW01 | (I/0) |          |

| 112              | Ext. Interrupt                   | 0116 | PSW10 |       |          |

|                  | Ext. Interrupt                   | 0016 | PSW11 |       |          |

|                  | Illegal Instruction              | 0716 | NONE  |       |          |

|                  | Privileged Instruction           | 0716 | PSW07 |       |          |

This interrupt can have several causes and is discussed further in I/O section.

# 4.4.3 Control Store Memory

The Model 80 can accommodate a maximum of 4K x 32 bits of control store memory. The computer allows data as well as instruction to be retrieved from its control memory. This capability expands its versatility by allowing data such as sine tables, translation tables and matrices to be stored and operated upon efficiently by the microprogrammer.

On models so equipped, the processor can alter its control store (write into its memory). This capability to store and retrieve data provides the power of a hardware computer at micro-instruction speeds.

ROM and dynamic control store can be mixed in 1K by 32 bit blocks.

## 4.4.4 Module Communications

Communication between the control and the internal modules is asynchronous. The internal logic of the CPU operates on a 10 MHz clock. This determines the fastest communication rate between modules.

A minimum of 2 clock periods (200ns) is necessary to complete an instruction, but the interchange time is dependent upon the external module and the length of time necessary for it to respond. The Control Module's clock is gated rather than free running to allow complete asynchronism between modules.

Module intercommunications is over a standard back panel allowing complete interchangability of card slots. Figure 4.3 illustrates the back panel links between modules.

FIGURE 4.3

#### 4.5 Arithmetic Module (ALU)

The ALU (arithmetic-logic unit) is a standard module in the Model 80. It is addressed as Module 1 and it can perform 20 functions.

By design, the ALU is never busy and for the majority of ALU functions, response is within 100 ns. (This allows most ALU instructions to be completed in 200ns.)

For functions which require more than one ALU cycle (i.e., shifts, rotates, multiply-divide), the ALU does not respond with a finish signal (MFIN) until the final results are on the S bus.

Multiply-divide and extended shift operations can be performed only on the 24 general registers and must address the same register pair on both the A & S bus. The same restrictions that apply to these operations on the Mod 5 must be observed in the Model 80.

A user emulated multiply-divide instruction is micro-coded by: selecting the ALU (module 1), addressing the UDR on the S bus, the UDRP1 (UDR plus 1) onto the A Bus, the USR onto the B Bus, and the required function code for the operation. When the ALU signals finish, the results have already been deposited in the UDR.

To implement a shift or rotate instruction, the register to be manipulated is addressed onto the A bus, the shift count is put onto the B bus, and the destination register is loaded from the S bus.

Extended shifts must address the UDRP1 (or equivalent) onto the A bus. The ALU performs its function as defined by the F field of the instruction:

| F FIELD | OPERATION                                |

|---------|------------------------------------------|

| 0000    | subtract                                 |

| 0001    | add                                      |

| 0010    | *subtract with carry (employs CPU flags) |

| 0011    | *add with carry (employs CPU flags)      |

| 0100    | not used                                 |

| 0101    | logical and                              |

| 0110    | logical exclusive or                     |

| 0111    | logical or                               |

| 1000    | *logical shift right                     |

| 1001    | *logical shift left                      |

| 1010 .  | *rotate right                            |

| 1001    | *rotate left                             |

| 1100    | *arithmetic shift right                  |

| 1101    | *arithmetic shift left                   |

| 1110    | *signed multiply                         |

| 1111    | signed divide                            |

<sup>\*</sup> When used in conjunction with the "K" bit of the RRC instruction, shifts are double precision, multiply is unsigned and the C, G and L of the PSW are used for add and subtract with carry.

The ALU employs its own gated asynchronous clock to perform the complex functions (shifts, multiply, divide). This is 10 MHz clock enabled by FSELO. The ALU is also allowed to manipulate the A and B buses, a priviledge reserved for it and the control module. The ST bus is generated on the ALU, which is the OR function of the S bus of the computer and the output of the ALU. The ST bus is the "true" source of all data to the registers designated as the S bus destination.

The ALU also manipulates the UDRP1 register for extended shift and multiply/divide instructions.

## 4.6 I/O Interface Board

The I/O Interface Board contains the I/O Module, the Display Controller and the TTY Controller. The I/O Module generates the Multiplexor Channel D-Bus from the CPU buses (A, B, S, CC, etc.) in addition to performing byte manipulation for the CPU and control of the Machine Control Register (MCR).

Controllers for the Display and TTY, located on the I/O Board, have access to the CPU via the Multiplexor Channel D-Bus.

# 4.6.1 Display Controller

The Display Controller makes use of the standard Model 70 Display Panel and provides the same operational features as the Model 70 Controller.

The Controller shares D-Bus drivers/receivers with the TTY Controller, and interrupts the CPU over the DSPLYO line provided.

#### 4.6.2 TTY Controller

The TTY Controller connects the Model 33/35 teletype to the Model 80 over the Multiplexor Channel. The Controller provides the serial/parallel conversion and all standard TTY control features in addition to a full character buffer in the receive mode. This allows program service in one character time (100 ms) instead of a bit time (9 ms).

## 4.6.3 I/O Module (See Figure 4.2)

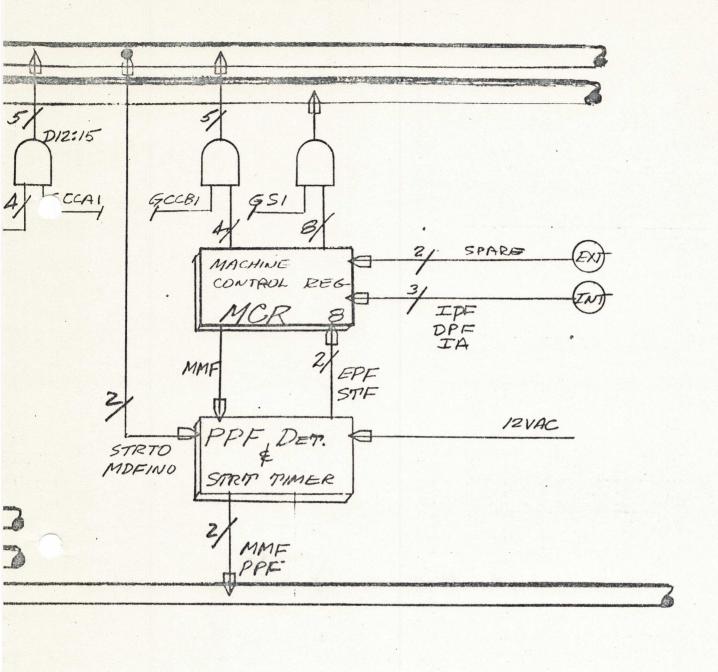

The I/O Module performs a multiplicity of functions. The main function is to generate a Mod 70 compatible Multiplexor Channel D-Bus from the CPU buses whenever it is addressed by module number 2 and the proper Function Selection is made. The module also performs byte manipulation for the CPU both in conjunction with an I/O operation and without. Finally, the I/O Module contains the Machine Control Register (MCR), which stores machine malfunction conditions, in addition to circuits for primary power fail detection, module STRT time out check and the generation of the Machine Malfunction (MMF) and Primary Power Fail (PPF) interrupts used by the CPU. The system initialize relay, which grounds the SCLRO line, is also located in the I/C Module.

The four Function Select lines together with the KSIG

line (see Fig. 5.1 for "K" bit) pick one of 32 possible functions, shown in the following table. The D-Bus functions may

be performed with or without an address cycle depending upon

the state of FSEL00. KSIG is used to specify register type

operations or, in the case of the halfword functions (RDH/WDH),

to specify the non D-Bus operations store block (STB) and load

block (LB).

FSELOX

|    | 0 | 1 | 2 | 3 |   | KSIG=0 |   | KSIG=1 |

|----|---|---|---|---|---|--------|---|--------|

| 0  | 0 | 0 | 0 | 0 |   | RD .   |   | RDR    |

| 1  | 0 | 0 | 0 | 1 |   | WD     |   | WDR    |

| 2  | 0 | 0 | 1 | 0 |   | SS     |   | SSR    |

| 3  | 0 | 0 | 1 | 1 |   | ос     |   | OCR    |

| 4  | 0 | 1 | 0 | 0 |   | RDH .  | * | STBR   |

| 5  | 0 | 1 | 0 | 1 |   | WDH    | * | LBR    |

| 6  | 0 | 1 | 1 | 0 |   |        |   | ACK    |

| 7  | 0 | 1 | 1 | 1 | * | SMCR   | * | CMCR   |

| 8  | 1 | 0 | 0 | 0 |   | RDA    |   | RDRA   |

| 9  | 1 | 0 | 0 | 1 |   | WDA    |   | WDRA   |

| A  | 1 | 0 | 1 | 0 |   | SSA    |   | SSRA   |

| В  | 1 | 0 | 1 | 1 |   | OCA    |   | OCRA   |

| С  | 1 | 1 | 0 | 0 |   | RDHA   | * | STB    |

| D  | 1 | 1 | 0 | 1 |   | WDHA   | * | LB     |

| Ε. | 1 | 1 | 1 | 0 | * | EXB    |   | DACK   |

| F  | 1 | 1 | 1 | 1 | * | POW    |   |        |

|    |   |   |   |   |   |        |   |        |

<sup>\*</sup> I/O INTERFACE OPERATION WITHOUT USE OF D-BUS

I/O Function Mnemonics are listed on the following table.

|    | MNEMO | NIC | MODULE FUNCTION            | COMMENT                                     |  |  |  |

|----|-------|-----|----------------------------|---------------------------------------------|--|--|--|

|    | RD    | *   | Read Data                  | byte/indexed type                           |  |  |  |

|    | WD    | *   | Write Data                 | byte/indexed type                           |  |  |  |

|    | oc    | *   | Output Command             | byte/indexed type                           |  |  |  |

|    | SS    | *   | Sense Status               | byte/indexed type                           |  |  |  |

|    | RDR   | *   | Read Data                  | byte/register type                          |  |  |  |

|    | WDR   | *   | Write Data                 | byte/register type                          |  |  |  |

|    | OCR   | *   | Output Command             | byte/register type                          |  |  |  |

|    | SSR   | * . | Sense Status               | byte/register type                          |  |  |  |

|    | ACK   |     | Acknowledge Interrupt      | byte/register type                          |  |  |  |

|    | RDH   | *   | Read Data Halfword         | 2 data cycles for byte controllers          |  |  |  |

|    | WDH * |     | Write Data Halfword        | 2 data cycles for byte controllers          |  |  |  |

|    | DACK  |     | Data Channel Acknowledge   | Includes an automatic                       |  |  |  |

| (* | ) RDA |     | Read Data                  | Same as RD but preceded by a device address |  |  |  |

|    | etc.  |     | etc.                       | cycle                                       |  |  |  |

|    | STB   |     | Store Byte                 | halfword/indexed type                       |  |  |  |

|    | LB    |     | Load Byte                  | byte/indexed type                           |  |  |  |

|    | STBR  |     | Store Byte                 | halfword/register type                      |  |  |  |

|    | LBR   |     | Load Byte                  | byte/register type                          |  |  |  |

|    | SMCR  |     | Sense Machine Control Reg. |                                             |  |  |  |

|    | CMCR  |     | Clear Machine Control Reg. |                                             |  |  |  |

|    | EXB   |     | Exchange B-Bytes           | B to S with byte                            |  |  |  |

|    | POW   |     | Release Initialize Relay   | exchange                                    |  |  |  |

|    |       |     |                            | 그는 현실이 가게 되는 때 이번 살아보다 하다면 하고 있다. 나라는       |  |  |  |

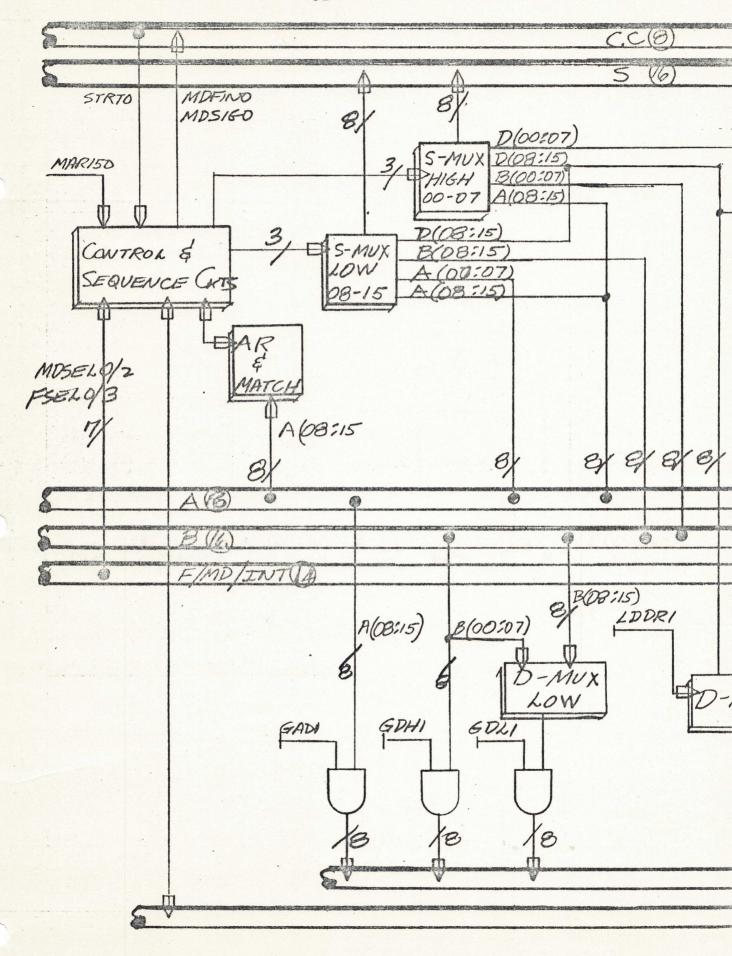

4.6.3.1 When the I/O Module is addressed and given an I/O function code, it creates a one, two or three cycle I/O operation. The device address on A(08:15) is gated to D(08:15) together with the ADRS control line whenever the address type of functions are specified. The returned SYN signal terminates the address cycle and the module sends the next control function (DA, DR, CMD or SR).

The halfword functions (RDH and WDH) will have a single data cycle when the Halfword (HW) test line is active and two data cycles when a byte oriented controller is addressed.

Output data is gated from the B-Bus to the D-Bus and the input data is gated from the D-Bus to the Data Register and then to the S-Bus.

At the end of the I/O operation, the I/O Module returns a MFIN signal to restart the CPU clock. The active state on the DCR and MSIG lines indicates that the data channel controller requests a memory read with the data readout sent to the channel on a subsequent WDH operation of the I/O Module. Should DCR not be active, the next step is a RDH operation of the I/O Module. At the end of the DACK operation, a control flip-flop is set which forces the HW test condition in the I/O Module to the active state. This permits proper execution of the following half-word function (RDH or WDH). This control flip-flop is cleared at the end of the halfword operation (or any other D-Bus operation that might have been given following the

DACK) .

An address cycle skip option is available which deletes the specified address cycle when the device specified is still addressed. A copy of the most recent device address is stored in the I/O Module to be checked against the next I/O address. Should they match, the device controller is still addressed and the I/O Module goes directly to the data cycle. For a mismatch, the ADRS cycle is generated and the address register is updated. The address register is cleared by the SCLRO or the DACK operation. It should be noted that this option does not produce the same sequence used in the Mod 5 and Mod 70. Since some device controllers may require special care in programming if this option is used, it is normally disabled, but is available to the user who wishes to utilize it.

4.6.3.2 A block diagram of the I/O Module is shown on Figure 4.2. The control and sequence circuit checks the module address and function code to set up the proper gating between buses. The multiplexors onto the S Bus are used for I/O operation as well as the byte manipulation between the A and B buses and the S Bus.

The PPF Detector checks the 12 VAC input and sets the early PPF (EPF) bit (15) in the MCR. After a suitable delay, the PPF interrupt is sent to the CPU.

The 35 us STRT timer is initiated whenever the module STRT signal leaves the CPU, and is cleared by the MDFIN signal from the module addressed. Should the timer time out before the MDFIN signal arrives, a malfunction exists; i.e., non-existant module, circuit trouble or no SYN signal from the D Bus. For an I/O operation, the false sync. code (0100) is placed on the CC bus and a false MFIN signal is generated to restart the CPU clock. With a module address other than the I/O module, the STF bit (10) in the MCR is set, the MMF interrupt is generated and a false MFIN is sent to restart the CPU clock,

The Machine Control Register (MCR) bit assignments are as follows:

| MCR15 | EPF | early primary power fail              |

|-------|-----|---------------------------------------|

| MCR14 | IPF | instruction parity fail (user memory) |

| MCR13 | DPF | data parity fail (user memory)        |

| MCR12 | MMF | set when any other MCR bit is set     |

| MCR11 | IA  | illegal address (user memory)         |

| MCR10 | STF | STRT Time fail                        |

| MCR09 |     | spare                                 |

| MCR08 |     | spare                                 |

The Sense MCR function code gates MCR (12:15) to the CC-Bus and MCR (08:15) to the S Bus. Another function code will clear the MCR.

I/O gating is summarized on the following table:

| -(0=)<br>7710 S                                                                                                | S(IE. HW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SELLOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BYTE CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RDHA &                    | HO                    | M        | 641 | FOR RD       | <b>⊗</b> |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|----------|-----|--------------|----------|

|                                                                                                                | and the state of t | HUTER &                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20725 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | - RELEAS                  | ×                     | X        | 1   | MOd          | 上        |

| HUSI ONA                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10000 & 2000<br>(4) S (4) |                       |          | -0  | DACK         | 3        |

|                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MAM LIET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SY DWS                    |                       | 1/0<br>X | -0  | BY WENT X    |          |

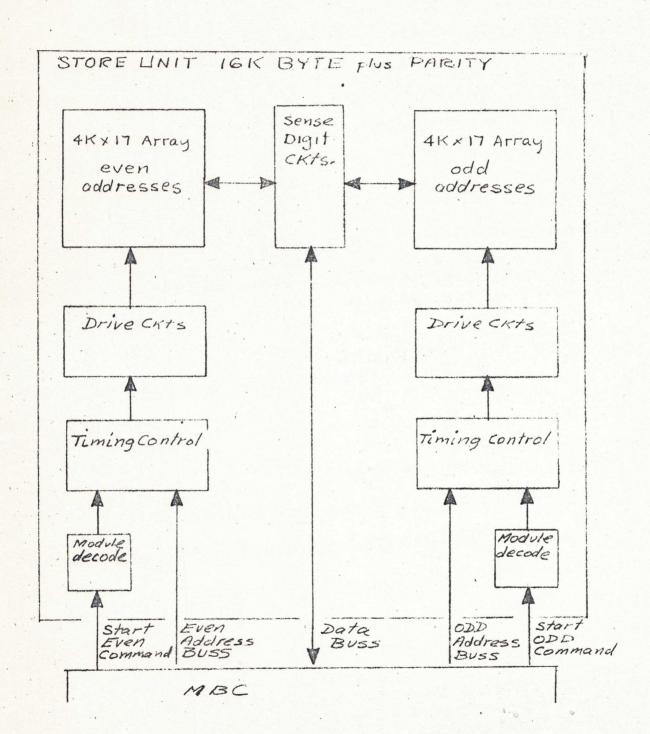

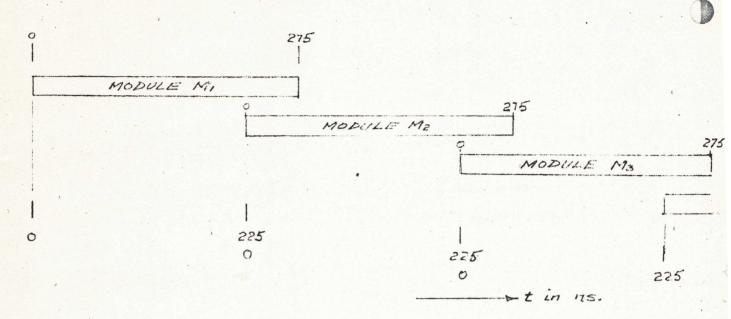

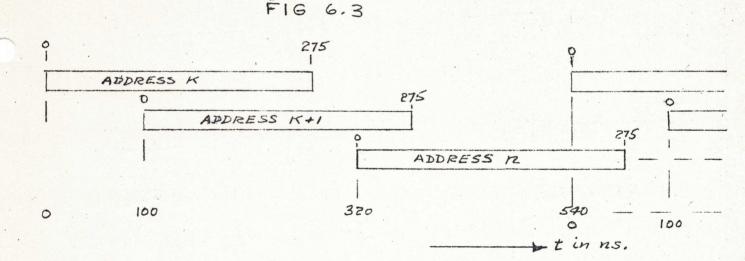

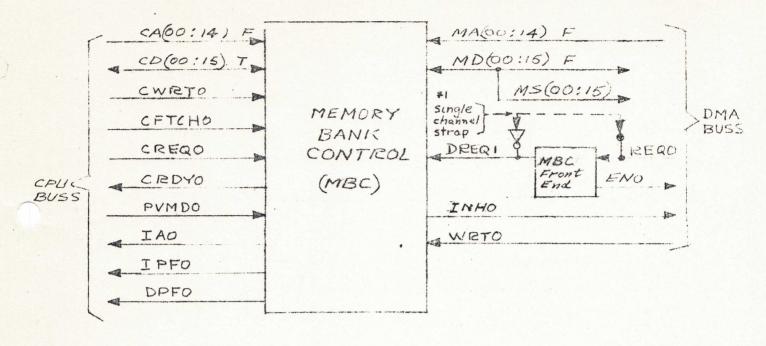

|                                                                                                                | (7)S 4-(7)V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1154 (H)B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | (7)5<-(7)8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (H)SK-(7)V                | X                     | 16       | 1   | 84S<br>VHON* | )        |